TÉLÉCHARGER ISE VHDL GRATUITEMENT

| Nom: | ise vhdl |

| Format: | Fichier D'archive |

| Système d'exploitation: | Windows, Mac, Android, iOS |

| Licence: | Usage Personnel Seulement |

| Taille: | 34.65 MBytes |

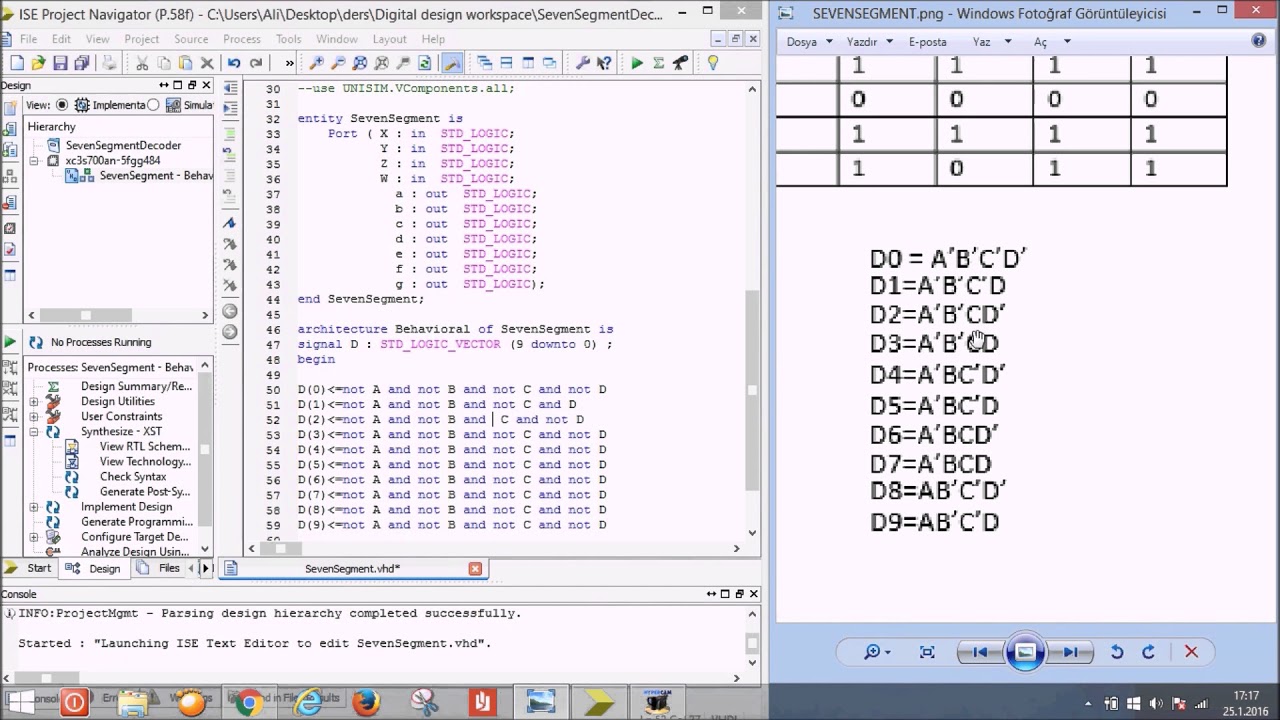

Son interface est la suivante: Nous allons dans un premier temps implémenter de manière hardware le design que nous avons conçcu ci-dessus. Conception électronique Langage informatique. Basculez en mode "avancé" pour parcourir l'ensemble des options. Pour cela sélectionnez votre fichier dans le panneau de gauche et dans les options en dessous, développez "ISim Simulator", ouvrez le menu contextuel sur "Simulate Behavioral Model" et sélectionnez "Process Properties Si vous développez ensuite "Synthetize — XST" vous verrez quelques options supplémentaires. On doit insérer la description du comportement entre la ligne begin et la ligne commençant par end.

Le comportement en simulation d'une telle écriture peut être différent de la première lorsque les entrées ont pour valeur X ou Z.

Nous allons calculer de deux façons les relations entre les sorties et les entrées, la première assignation avec 2 bascules T et la seconde avec 2 bascules JK. En effet, avec l'assertion not LD0 nous essayons de relire l'état de la sortie LD0.

Vous pouvez alors programmer directement votre carte via USB. Quartus II Web Edition [ 5 ]. La fenêtre qui s'ouvre alors doit être celle-ci:.

Si vous souhaitez utiliser Adept, je vous invite à suivre la procédure décrite dans le guide utilisateur qui se trouve normalement à un emplacement de ce type: On devrait maintenant voir qu'un vhhdl a été ajouter dans la section des fichiers source sous l'icône représentant le FPGA.

Performances

L'étape suivante consiste à synthétiser cette description matérielle pour obtenir un composant réalisant les fonctions désirées, à l'aide d' éléments logiques concrets portes logiquesbascules ou registres. D'après les spécifications énoncées ci-dessus, le jouet robot a 4 états possibles: Modifier l'ensemble de l'architecture comme suit:.

La version initiale de VHDL, standard IEEEincluait un large éventail de types de données, numériques entiers, réelslogiques bitsbooléenscaractères, temps, plus les tableaux de bits et isw de caractères. Vous pouvez descendre dans l'architecture en double-cliquant sur une entité. Elles nous permettront d'envoyer et de recevoir des signaux depuis la carte.

Avant de passez à la suite, nous allons créer notre fichier qui contiendra les valeurs de la ROM. Ce tutoriel a pour but de vous présenter l'environnement de développement et des premiers exemples de codes VHDL. Vous pouvez retrouver dans cette liste la quasi-totalité des syntaxes que l'on peut retrouver en VHDL. Le but de la modification est donc de détecter un changement d'état sur le bouton passage de appuyé à relâché. Supprimez dans un premier temps notre ancienne ligne de code:.

Cette librairie permet d'instancier différents blocs de base matériels du CPLD.

Programmation FPGA sur carte Xilinx Spartan-6 (Nexys 3)

Mines ParisTech 3 -- Engineer: Cette page vous donne un aperçu rapide du taux d'occupation du Ies et un compte-rendu des ressources. Il ne vous reste plus qu'à programmer le composant, testez votre design sur la carte et à écrire vos propres programmes!

Le fichier est créé en cliquant sur Finish. En bas se trouve la "Console". Lorsqu'il s'agit d'écrire un modèle comportemental qui sera simplement simulé, le langage est compilé puis exécuté par le simulateur.

Changeons les paramètres de la simulation. Lancez ensuite en double-cliquant sur "Simulate Behavioral Model". Laissez les options comme vous les avez trouvé et fermez la fenêtre. Certaines contraintes ne servent qu'aux calculs de timing dans le design. En relisant le code de notre fichier "Top", on peut voir que le comportement que nous ie décrit est le suivant: Le VHDL ayant une double fonction simulation et synthèseune partie seulement du VHDL est synthétisable, l'autre existant uniquement pour faciliter la simulation écriture de modèles comportementaux et de test benches.

Le jouet doit fonctionner de la façon suivante: Certaines contraintes peuvent être indiquées dans le code à l'aide d'attributs. Ce fichier a l'extension.

Vous avez deux panneaux principaux dans la fenêtre de l'application. Si vous laissez le bouton de votre souris appuyé et que vous tirez le curseur, vous pouvez mesurer une durée.

Comments

Post a Comment